## 4ch 32Bit High-Speed Up/Down Counter Board for Low Profile PCI (TTL Input)

#### CNT32-4MT(LPCI)

\* Specifications, color and design of the products are subject to change without notice.

#### **Features**

Can input two-phase and single-phase signals.

Can input pulse signals up to 10MHz and can resolve phase differences as short as 25nsec.

Can be converted to a differential input interface using the differential unit (CTP-4D) and connection cable (CNT-68M/50M) which are sold separately.

One control signal input pin per channel.

Can count values sampling at a maximum sampling rate of 20 MHz.

Supporting bus mastering, enabling high-speed data transfer between the board and the PC without intervention from the CPU.

Can generate an interrupt, issuing an external signal, or presetting/zero-clearing the count value when it matches an arbitrary predefined value.

Support for both of low-profile and standard PCI slots (interchangeable with a bundled bracket).

This is a PCI bus compliant interface board for counting the pulses input from the external device.

The board supports a low-profile PCI slot and, if replaced with the supplied bracket, supports a PCI slot, too.

The board has four channels of 32-bit up/down counters, allowing external devices such as a rotary encoder and a linear scale to be connected. Given below are examples of using the board for "detecting a position of the table of a machine tool" and "detecting a change in weight".

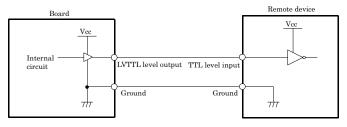

The pulse signal inputting interface is unisolated LVTTL-level input that can input pulse signals at high speed.

The application for this board can transfer data between the board and the PC at high speed using PCI bus mastering.

#### <Example >

#### **Specification**

#### <1/2>

| 1 / 2 >                                          | Specification                                             |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------|--|--|--|

| ut                                               | '                                                         |  |  |  |

| Counter                                          |                                                           |  |  |  |

| Channel count                                    | 4 channels                                                |  |  |  |

| Count system                                     | Up/down counting                                          |  |  |  |

|                                                  | (2-phase/Single-phase/Single-phase Input with Gate        |  |  |  |

|                                                  | Control Attached)                                         |  |  |  |

| Max. count                                       | FFFFFFFh(binary data, 32Bit) Unisolated LVTTL level input |  |  |  |

| Input type                                       |                                                           |  |  |  |

|                                                  | Phase-A/UP 1 x 4 channels                                 |  |  |  |

| Input signal                                     | Phase-B/DOWN 1 x 4 channels                               |  |  |  |

|                                                  | Phase-Z/CLR 1 x 4 channels<br>10MHz 50% duty              |  |  |  |

| Response frequency                               |                                                           |  |  |  |

| Digital filter                                   | 0.1μsec - 1.6384msec or not used                          |  |  |  |

|                                                  | (can be independently set for each channel.)              |  |  |  |

| Timer                                            | 1msec - 6553msec 1msec unit                               |  |  |  |

| Counter start trigger                            | Software/External start input/Sampling start trigger      |  |  |  |

| Counter stop trigger                             | Software/External stop input/Sampling stop trigger        |  |  |  |

| Sampling                                         | 1                                                         |  |  |  |

| Sampling start trigger                           | Software/External start input/Count match                 |  |  |  |

| Camping start trigger                            | Software/External stop input/Specification number/Bus     |  |  |  |

| Sampling stop trigger                            | master tranfer error/Count match                          |  |  |  |

| Sampling clock                                   | Sampling timer/External clock input                       |  |  |  |

| Sampling timer                                   | 50nsec - 107sec 25nsec unit(can not be independently      |  |  |  |

| Camping amo                                      | set for each channel.)                                    |  |  |  |

| External sampling start                          | Unisolated LVTTL level input (Select Rise or Fall)        |  |  |  |

| signal                                           | oniosiated 21112 is to impat (osiost 1 tips of 1 dill)    |  |  |  |

| External sampling stop                           | Unisolated LVTTL level input (Select Rise or Fall)        |  |  |  |

| signal                                           | Offisolated EV FFE level input (Oelect Nise of Fail)      |  |  |  |

| External sampling clock                          | Unisolated LVTTL level input (Fall)                       |  |  |  |

| signal                                           | , , , , , , , , , , , , , , , , , , , ,                   |  |  |  |

| Response frequency                               | 10MHz 50% duty                                            |  |  |  |

| Control                                          | 1                                                         |  |  |  |

| Control input signal type                        | Unisolated LVTTL level input                              |  |  |  |

| Control input channel                            | 1 x 4 channels                                            |  |  |  |

|                                                  | - Preset(Select Rise or Fall)                             |  |  |  |

|                                                  | - Zero-clear(Select Rise or Fall)                         |  |  |  |

| Control input signal                             | - Counter start/stop(Select Rise or Fall)                 |  |  |  |

|                                                  | - General-purpose input(positive logic)                   |  |  |  |

|                                                  | Software-selected from among the above four options       |  |  |  |

| Response time                                    | 100nsec (Max.)                                            |  |  |  |

| <del>-                                    </del> | Count match(8 points), Counter error(2 points), Samplin   |  |  |  |

| Interrupt event                                  | [Court match(o points), Courter error(2 points). Sambiir  |  |  |  |

#### < 2 / 2 >

|                       | Item                  | Specification                                                                                                                                                                                          |  |  |  |  |

|-----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| utput                 |                       |                                                                                                                                                                                                        |  |  |  |  |

| Control               |                       |                                                                                                                                                                                                        |  |  |  |  |

|                       | Control output signal | Unisolated LVTTL level output                                                                                                                                                                          |  |  |  |  |

|                       | type                  | _                                                                                                                                                                                                      |  |  |  |  |

|                       | Control output        | 1 x 4 channels                                                                                                                                                                                         |  |  |  |  |

|                       | channel               |                                                                                                                                                                                                        |  |  |  |  |

|                       |                       | - Count match 0 output(one-shot pulse output)                                                                                                                                                          |  |  |  |  |

|                       |                       | - Count match 1 output(one-shot pulse output)                                                                                                                                                          |  |  |  |  |

|                       |                       | Digital filter error output(one-shot pulse output)     Abnormal input error output(one-shot pulse output)     General-purpose output(Level output) Software-selected from among the above five options |  |  |  |  |

|                       | Control output signal |                                                                                                                                                                                                        |  |  |  |  |

|                       |                       |                                                                                                                                                                                                        |  |  |  |  |

|                       |                       |                                                                                                                                                                                                        |  |  |  |  |

|                       |                       | (Positive/negative logic is selected with the software.)                                                                                                                                               |  |  |  |  |

|                       |                       | Selected between 10μsec, 100μsec, 1msec, 10msec and                                                                                                                                                    |  |  |  |  |

|                       | One shot output       | 100 msec (Can be set for each channel, within precision + 1μsec)                                                                                                                                       |  |  |  |  |

|                       | signal amplitude      |                                                                                                                                                                                                        |  |  |  |  |

|                       | Response time         | 100nsec (Max.)                                                                                                                                                                                         |  |  |  |  |

|                       | Rated output current  | , ,                                                                                                                                                                                                    |  |  |  |  |

| Test pu               |                       | IOL-OTH (Max.)                                                                                                                                                                                         |  |  |  |  |

| Test pu               | Test pulse output     | Unisolated LVTTL level output                                                                                                                                                                          |  |  |  |  |

|                       | signal type           | Onisolated LV FFE level output                                                                                                                                                                         |  |  |  |  |

|                       |                       | One for each of phases A and B                                                                                                                                                                         |  |  |  |  |

|                       | Test pulse output     | One for each of phases-A and B                                                                                                                                                                         |  |  |  |  |

|                       | point                 | 400111 6                                                                                                                                                                                               |  |  |  |  |

|                       | Output frequency      | 100kHz fixed                                                                                                                                                                                           |  |  |  |  |

| Sampli                |                       |                                                                                                                                                                                                        |  |  |  |  |

|                       | Sampling output       | Unisolated LVTTL level output                                                                                                                                                                          |  |  |  |  |

|                       | signal type           |                                                                                                                                                                                                        |  |  |  |  |

|                       | Output point          | Sampling start trigger, sampling stop trigger,                                                                                                                                                         |  |  |  |  |

|                       |                       | Sampling clock trigger 1 point each                                                                                                                                                                    |  |  |  |  |

|                       | One-shot output       | Negative logic 100nsec (fixed)                                                                                                                                                                         |  |  |  |  |

|                       | signal width          |                                                                                                                                                                                                        |  |  |  |  |

|                       | Response speed        | 100nsec (Max.)                                                                                                                                                                                         |  |  |  |  |

|                       | Rated output current  | $I_{OL} = 8mA(Max.)$ $I_{OH} = -8mA(Max.)$                                                                                                                                                             |  |  |  |  |

| us master             |                       |                                                                                                                                                                                                        |  |  |  |  |

| DMA ch                | nannel                | 1 channel                                                                                                                                                                                              |  |  |  |  |

| Transfe               | er bus width          | 32-Bit width                                                                                                                                                                                           |  |  |  |  |

|                       | er data length        | 8 PCI Words length(Max.)                                                                                                                                                                               |  |  |  |  |

| Transfe               |                       | 80MB/sec(Max.133MB/sec)                                                                                                                                                                                |  |  |  |  |

| FIFO                  |                       | 1K-DWord                                                                                                                                                                                               |  |  |  |  |

|                       | /Gather function      |                                                                                                                                                                                                        |  |  |  |  |

|                       |                       | 64MB                                                                                                                                                                                                   |  |  |  |  |

|                       | ot event              | Bus master event(7 points)                                                                                                                                                                             |  |  |  |  |

| ommon                 |                       | <u></u>                                                                                                                                                                                                |  |  |  |  |

| I/O add               |                       | Occupies 2 locations, any 32-bytets and 64-byte boundary                                                                                                                                               |  |  |  |  |

| Power                 | consumption           | 5VDC 300mA (Max.)                                                                                                                                                                                      |  |  |  |  |

| Operat                | ing condition         | 0 - 50°C, 10 - 90%RH (No condensation)                                                                                                                                                                 |  |  |  |  |

| PCI bus specification |                       | 33bit, 33MHz, Universal key shapes supported *1                                                                                                                                                        |  |  |  |  |

| PCI bu                | 3 Specification       | country company company                                                                                                                                                                                |  |  |  |  |

|                       | sion (mm)             | 121.69(L) x 63.41 (H)                                                                                                                                                                                  |  |  |  |  |

This board requires power supply at +5 V from an expansion slot (it does not work on a machine with a +3.3-V power supply alone).

#### **Support Software**

#### Driver Library API-PAC(W32) (Bundled)

API-PAC(W32) is the library software that provides the commands for CONTEC hardware products in the form of Windows standard Win32 API functions (DLL). It makes it easy to create high-speed application software taking advantage of the CONTEC hardware using various programming languages that support Win32 API functions, such as Visual Basic and Visual C/C++.

It can also be used by the installed diagnosis program to check hardware operations.

CONTEC provides download services to supply the updated drivers and differential files.

For details, read Help on the bundled CD-ROM or visit the CONTEC's Web site.

< Operating environment >

OS Windows XP, 2000, Me, 98, etc..

Adaptation language Visual C/C++, Visual Basic, Delphi,

Builder, etc..

Others Each piece of library software requires

50 MB of free hard disk space.

#### Cable & Connector

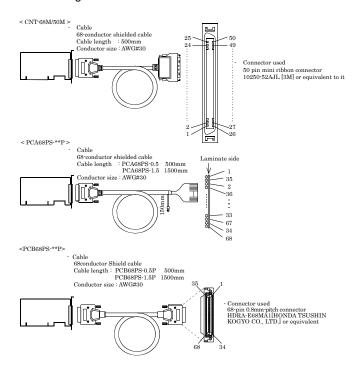

#### Cable(Option)

Shielded cable for CardBus counter input card

: CNT-68M/50M (0.5m)

Cable with 68-Pin D-sub Connector

at either Ends (Mold Type) : PCB68PS-0.5P (0.5m)

: PCB68PS-1.5P (1.5m)

Shielded cable with single connector

: PCA68PS-0.5P for 68-pin 0.8mm pitch connector (0.5m)

: PCA68PS-1.5P (1.5m)

#### **Accessories**

#### **Accessories (Option)**

Termination Panel with Differential Receivers

for Counter Input : CTP-4D \*1 Screw Terminal (M3 x 50P) : EPD-50A \*1 Screw Terminal (M3 x 68) : EPD-68A \*2

- CNT-68M/50M optional cable is required separately. PCB68PS-0.5P or PCB68PS-1.5P optional cable is required separately.

- Check the CONTEC's Web site for more information on these options.

#### **Packing List**

Board [CNT32-4MT(LPCI)] ...1 First step guide ... 1 CD-ROM \*1 [API-PAC(W32)] ...1 Bracket for PCI...1

\*1 The CD-ROM contains the driver software and User's Guide.

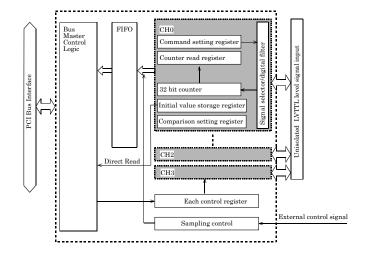

### **Block Diagram**

#### **Using the On- Board Connectors**

#### Connecting a Board to a Connector

Use the optional connection cable (CNT-68M/50M or PCA68PS-\*\*P, PCB68PS-\*\*P) to connect the board to an external device. Uses the cable together with a terminal block for the wiring between the board and external device.

#### **Connector Pin Assignment**

#### Pin Assignment of an interface connector(CN1)(Board side)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                                                               | _                                                                                      |                                                                                                                                                                 |                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH0 phase A input CH0 Phase B input CH0 Phase B input CH0 Control input *1 Unconnection CH1 Phase A input CH1 Phase B input CH1 Phase B input CH1 Phase B input CH1 CH1 Unconnection CH2 Phase A input CH2 Phase B input CH2 Phase B input CH2 CONTROL INPUT CH2 CONTROL INPUT CH2 CONTROL INPUT CH2 CONTROL INPUT CH3 CONTROL | A0 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | 35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49 | - GND<br>- GND<br>- GND<br>- GND<br>- N.C.<br>- GND<br>- GND | Ground Ground Ground Unconnection Ground |

| CH2 Phase-A input<br>CH2 Phase-B input<br>CH2 Phase-Z input<br>CH2 control input *1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A2 | 11<br>12<br>13<br>14                                                          | 45 46 47 48 49 50 51 55 56 57 60 61 62 63 64 65 66 67                                  | - GND<br>- GND<br>- GND<br>- GND<br>- GND<br>- GND<br>- GND<br>- GND<br>- GND<br>- N.C.<br>- GND<br>- STARTIN<br>- N.C.<br>- GND                                | Ground<br>Ground<br>Ground<br>Ground                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (  | _                                                                             | _                                                                                      |                                                                                                                                                                 | * '                                                                                                                                                                                                              |

- \*1 The control input can serve as the general-input, counter start/stop, preset, and zero-clear.

\*2 The control output can serve as the general-output, count match, abnormal input error and digital filter error.

\*3 Supply-capable current is 500mA (Max.).

- Pin Assignment of CNT-68M/50M

Co

#### +3.3V Output \*3 Counter Input signal pull-up CH2 control output \*2 CH0 control output \*2 +3.3V Output \*3 Counter Input signal pull-up CH3 control output \*2 CH1 control output \*2 $\begin{array}{c} 25 \\ 24 \\ 23 \\ 22 \\ 21 \\ 20 \\ 19 \\ 18 \\ 17 \\ 16 \\ 15 \\ 14 \\ 13 \\ 12 \\ 11 \\ 10 \\ 9 \\ 8 \\ 7 \\ 6 \\ 5 \end{array}$ CH2 control output \*2 Test pulse Phase A output Sampling Stop Output Sampling Stop Output Sampling Clock Output Sampling Clock Output Sampling Clock Input CH3 Control Input \*1 CH3 Phase B input CH3 Phase B input CH3 Phase B input CH2 Control Input \*1 CH2 Phase B input CH2 Phase B input CH2 Phase B input CH2 Phase A input CH3 Phase A input CH4 Phase B input CH4 Phase B input CH6 Phase B input AGND AI 04 N.C. AI 05 N.C. TPOB STARTOUT GND STARTIN GND Test pulse Phase-B outp Sampling Start Output Ground Sampling Start Input Ground 44 43 42 41 $\frac{40}{39}$ AO START AO STOP AO EXCLK DGND $\begin{array}{c} 38 \\ 37 \\ 36 \\ 35 \\ 34 \\ 33 \\ 32 \\ 31 \\ 30 \\ 29 \\ \end{array}$ DGNE CNT UPCLE

\*1 The control input can serve as the general-input, counter start/stop, preset, and zero-clear.

\*2 The control output can serve as the general-output, count match, abnormal input error and digital filter error.

\*3 Supply-capable current is 500mA (MaX).

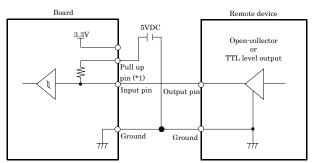

#### **How to Connect the Counter Input Signal**

You can connect to a rotary encoder or linear scale with a TTL level output circuit, or to an open-collector output circuit. The signal must be an LVTTL level input and can be up to 10MHz. As pull-up resisters are provided on the board, connect the pull-up voltage (3.3V to 5.5V max.) to the pull-up pins if connecting to an open collector output circuit/TTL-level output circuit. (If using 3.3V, connect to the VCC pin on the board.) Not connecting the pull-up voltage may affect the counter input channel left unconnected.

For a two-phase input, connect both phase A and phase B. For a single phase input, connect to either phase A or phase B. If not using the Z phase, this does not need to be connected.

#### Remarks

The pull-up pins are PUP1 (pin 32 \*1) for the counter input signal and PUP2 (pin 66 \*1) for the control input signal. PUP1 (pin 32):

> Pull-up for A, B, and Z phase input signal (A0, B0, Z0, A1, B1, Z1, A2, B2, Z2, A3, B3, Z3).

PUP2 (pin 66):

Pull-up for the control input signals and for the sampling input signals

(DI0, DI1, DI2, DI3, CLKIN, STARTIN, STOPIN).

\*1 Connector pin number on the board.

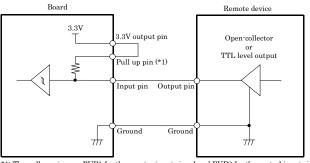

#### **Example Connection for Counter Input Circuit** Connection pulled up with external 5-V power (Counter Input)

\*1: The pull-up pins are PUP1 for the counter input signal and PUP2 for the control input signal.

#### Connection pulled up with internal 3.3-V output power (Counter Input)

\*1: The pull-up pins are PUP1 for the counter input signal and PUP2 for the control input signal.

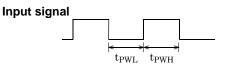

tpwh: High-level count input pulse width 50nsec (Min.) tpwi.: Low-level count input pulse width 50nsec (Min.)

#### **↑** CAUTION

The connection cable length should be within 1.5 m.

To prevent noise from causing a malfunction, arrange the connection cable as away from any other signal conductor or noise source as possible.

## Connecting the control signal input/output

#### Connection of a control input

The control input signals consist of one pin per channel that can be selected as the channel's counter start/stop or preset, and one pin per board that can be used as the start, stop, and clock for sampling. The signals are LVTTL-level inputs.

As pull-up resisters ( $10 \text{K}\Omega$ ) are provided on the board, connect the pull-up voltage (3.0 V to 5.5 V max.) to the pull-up pins if connecting to an open collector output circuit/TTL-level output circuit. (If using 3.3 V, connect to the VCC pin on the board.) Not connecting the pull-up voltage may affect the control input pin left unconnected.

#### Remarks

The pull-up pins are PUP1 (pin 32 \*1) for the counter input signal and PUP2 (pin 66 \*1) for the control input signal. PUP1 (pin 32):

Pull-up for A, B, and Z phase input signal (A0, B0, Z0, A1, B1, Z1, A2, B2, Z2, A3, B3, Z3). PUP2 (pin 66):

Pull-up for the control input signals and for the sampling input signals

(DIO, DI1, DI2, DI3, CLKIN, STARTIN, STOPIN).

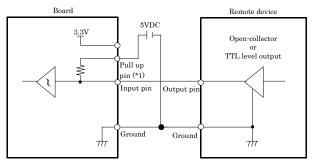

# Control input circuit and its sample connection Connection pulled up with external 5-V power (Control input DI0, DI1, DI2, DI3, CLKIN, STARTIN, STOPIN)

$<sup>^{\</sup>star}1^{:}$  The pull-up pins are PUP1 for the counter input signal and PUP2 for the control input signal.

## Connection pulled up with internal 3.3-V output power (Control input DI0, DI1, DI2, DI3, CLKIN, STARTIN, STOPIN)

\*1: The pull-up pins are PUP1 for the counter input signal and PUP2 for the control input signal.

#### **⚠** CAUTION

The connection cable length should be within 1.5 m.

To prevent noise from causing a malfunction, arrange the connection cable as away from any other signal conductor or noise source as possible.

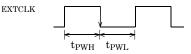

#### External sampling clock signal (EXTCLK)

Pin used to input the external pacer clock. The maximum frequency is 10MHz.

If the external clock input is selected as the sampling clock, sampling occurs on the falling edge of the signal.

$t_{PWH}: \mbox{ High-level clock pulse width 50nsec (Min.)} \\ t_{PWL}: \mbox{ Low-level clock pulse width 50nsec (Min.)}$

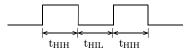

## Other control input signals (DI0 to DI3, EXTSTART, EXTSTOP)

These signals are TTL-level compatible and the trigger edge is software-programmable at either the rising or falling edge. High- and low-level hold times of at least 50 nsec are required to detect an edge of the signal.

$\begin{array}{ll} t_{HIIH}: & \mbox{High-level hold time 50nsec (Min.)} \\ t_{HIIL}: & \mbox{Low-level hold time 50nsec (Min.)} \end{array}$

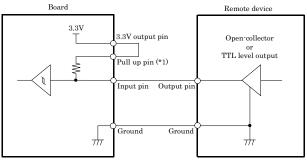

#### Connection of a control output

This outputs a general-purpose output signal (level output) or a one-shot pulse output to indicate a hardware event such as a count match. The signal is an LVTTL level output and can be set to positive or negative logic by software.

#### Control output circuit and its sample connection

<sup>\*1</sup> Connector pin number on the board.